In modern FPGA and ASIC design, the logic you write inside a module is often less important than how that module talks to the rest of the system. You cannot just wire a CPU to a DDR controller directly; you need a standardized language—a protocol.

The industry is dominated by a handful of standards, most notably from ARM’s AMBA (Advanced Microcontroller Bus Architecture) family and the open-source community. A common mistake is defaulting to the most complex protocol (AXI) for every connection, wasting area and complicating verification.

Choosing the right protocol is a trade-off between Throughput, Latency, and Area/Complexity. Let’s break down the four players you will encounter most often.

1. AXI (Advanced eXtensible Interface): The High-Performance Beast

Origin: ARM AMBA 3/4

Best For: High-bandwidth connections (CPU to DDR, DMA engines, PCIe).

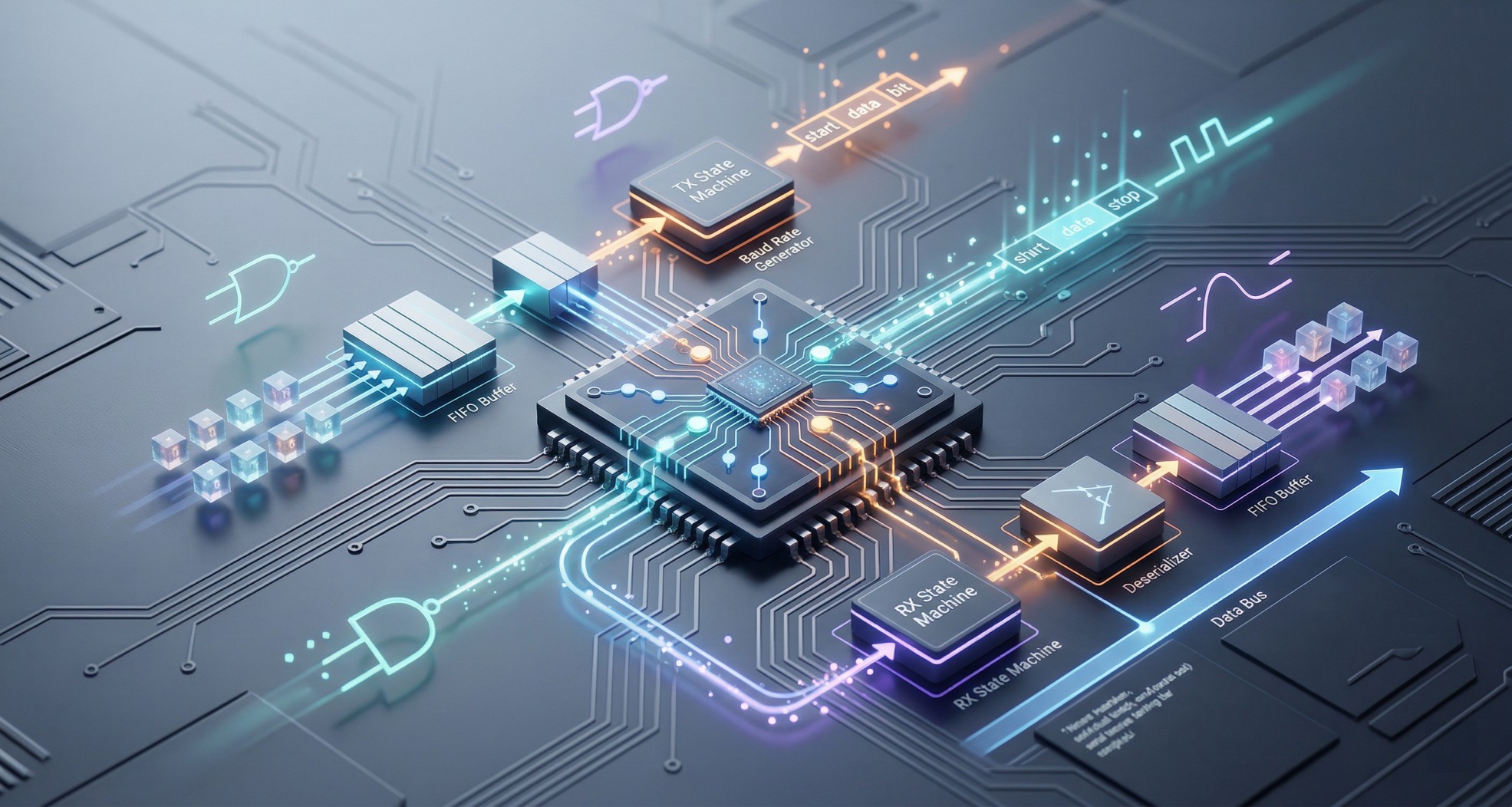

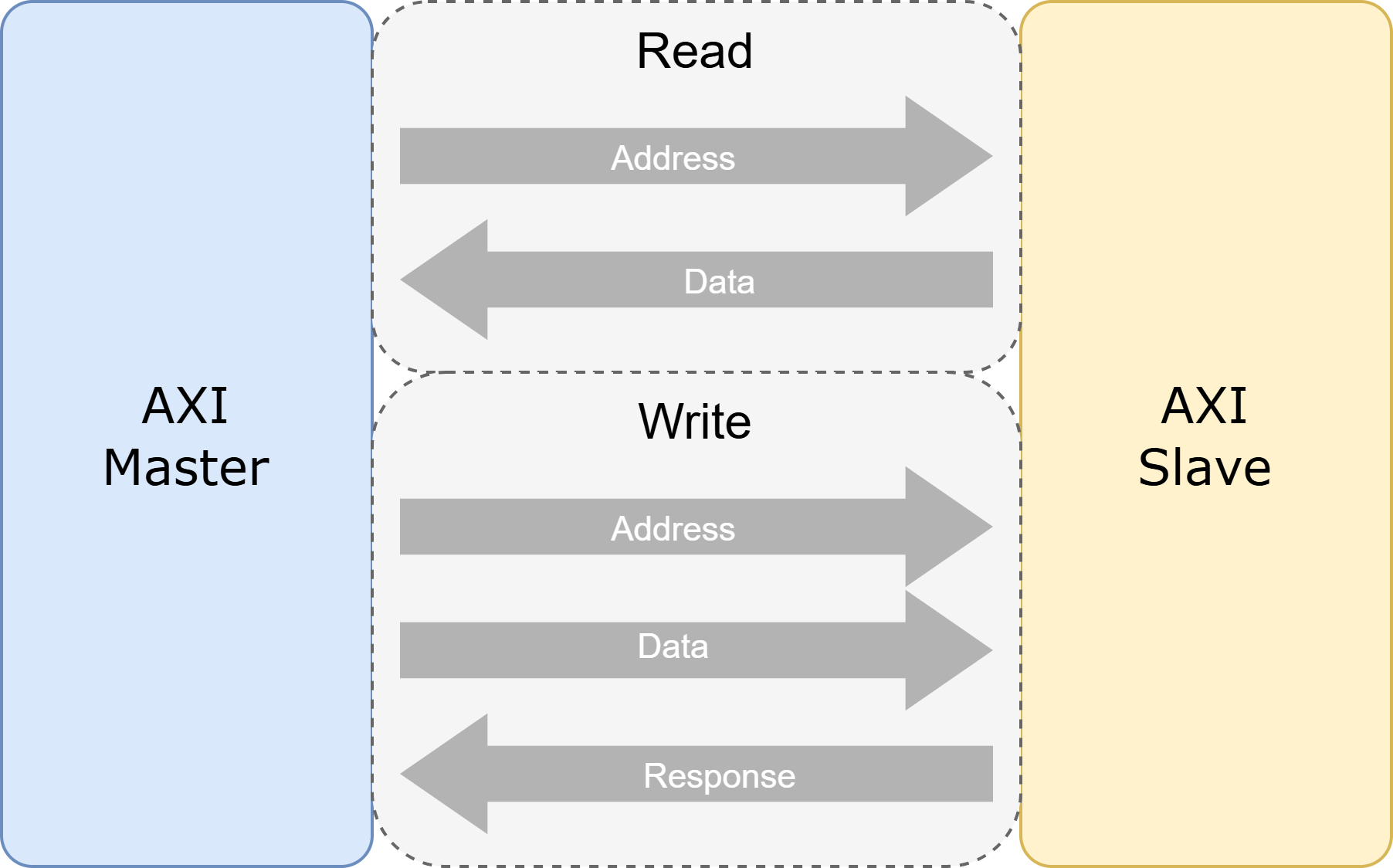

AXI is the current gold standard for performance. Its key feature is the separation of Read and Write channels. Unlike simpler buses, address and data phases are decoupled. This allows for multiple outstanding transactions—you can issue 10 read requests back-to-back without waiting for the first one to return data.

- Pros: Highest throughput, supports out-of-order transaction completion, separate read/write channels enable full-duplex communication.

- Cons: High signal count (complexity), significant silicon area for interconnect logic (crossbars), higher latency for simple single transactions due to protocol overhead.

2. AHB (Advanced High-performance Bus): The Classic Workhorse

Origin: ARM AMBA 2

Best For: Medium-performance system backbones, connecting on-chip RAMs, and simpler masters.

Before AXI, AHB was the king. It is a single-channel, pipelined bus. “Pipelined” means the address phase of transaction N+1 can occur during the data phase of transaction N. It supports burst transfers but does not support multiple outstanding transactions or out-of-order completion.

- Pros: Lower latency than AXI for single transfers, simpler interface, well-suited for on-chip memories (BRAM/SRAM) which have fixed latency.

- Cons: Shared read/write data bus limits throughput (half-duplex), cannot hide high-latency operations (like DDR access) efficiently.

3. APB (Advanced Peripheral Bus): The Low-Power Specialist

Origin: ARM AMBA

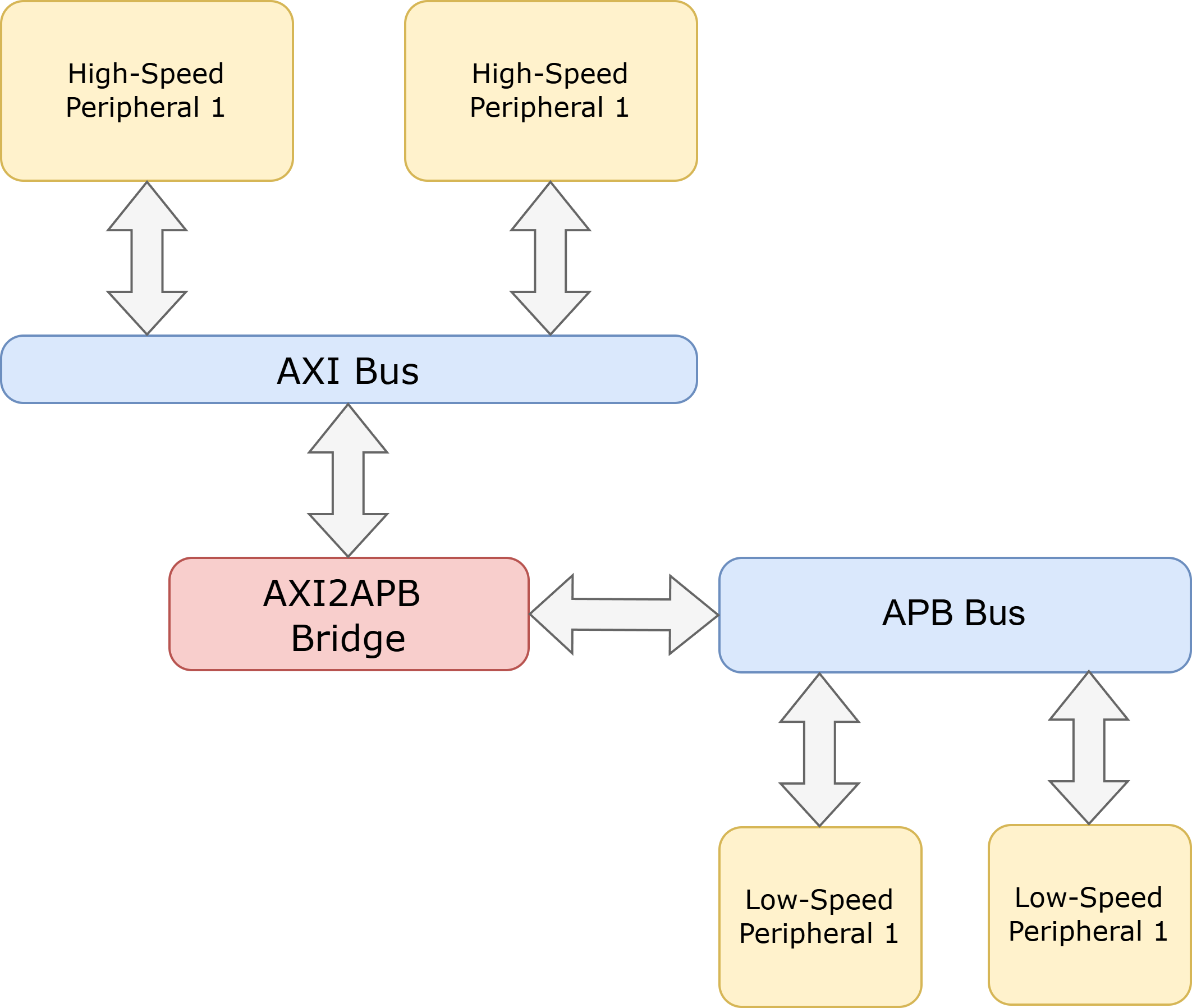

Best For: Configuration registers of peripherals (UART, SPI, Timers, GPIO).

APB is designed for simplicity and low power, not speed. It is non-pipelined. Every transaction takes at least two cycles: a Setup phase and an Access phase. It is almost always used as a “leaf node” on the system bus, connected to a faster bus (like AXI or AHB) via a bridge.

- Pros: Extremely simple interface (very few signals), minimal silicon area, very easy to verify.

- Cons: Very low bandwidth, high latency (min 2 cycles), no burst support.

4. Wishbone: The Open-Source Alternative

Origin: OpenCores Community

Best For: Open-source projects, FPGA-to-FPGA communication, simple custom IP cores.

Wishbone is unique because it is not owned by a corporation like ARM. It is a very flexible, open standard. It can be configured to be as simple as APB or as complex as a pipelined AHB depending on the signals you choose to implement. Its handshake mechanism (CYC, STB, ACK) is simple and robust.

- Pros: Completely free and open license, highly flexible, simpler handshake than AMBA protocols, widely used in the open-source FPGA community (e.g., RISC-V cores like SERV or VexRiscv).

- Cons: Less adoption in commercial ASIC toolchains compared to AMBA, ecosystem is fragmented due to its flexibility (not all Wishbone cores are instantly compatible).

Summary & Decision Matrix

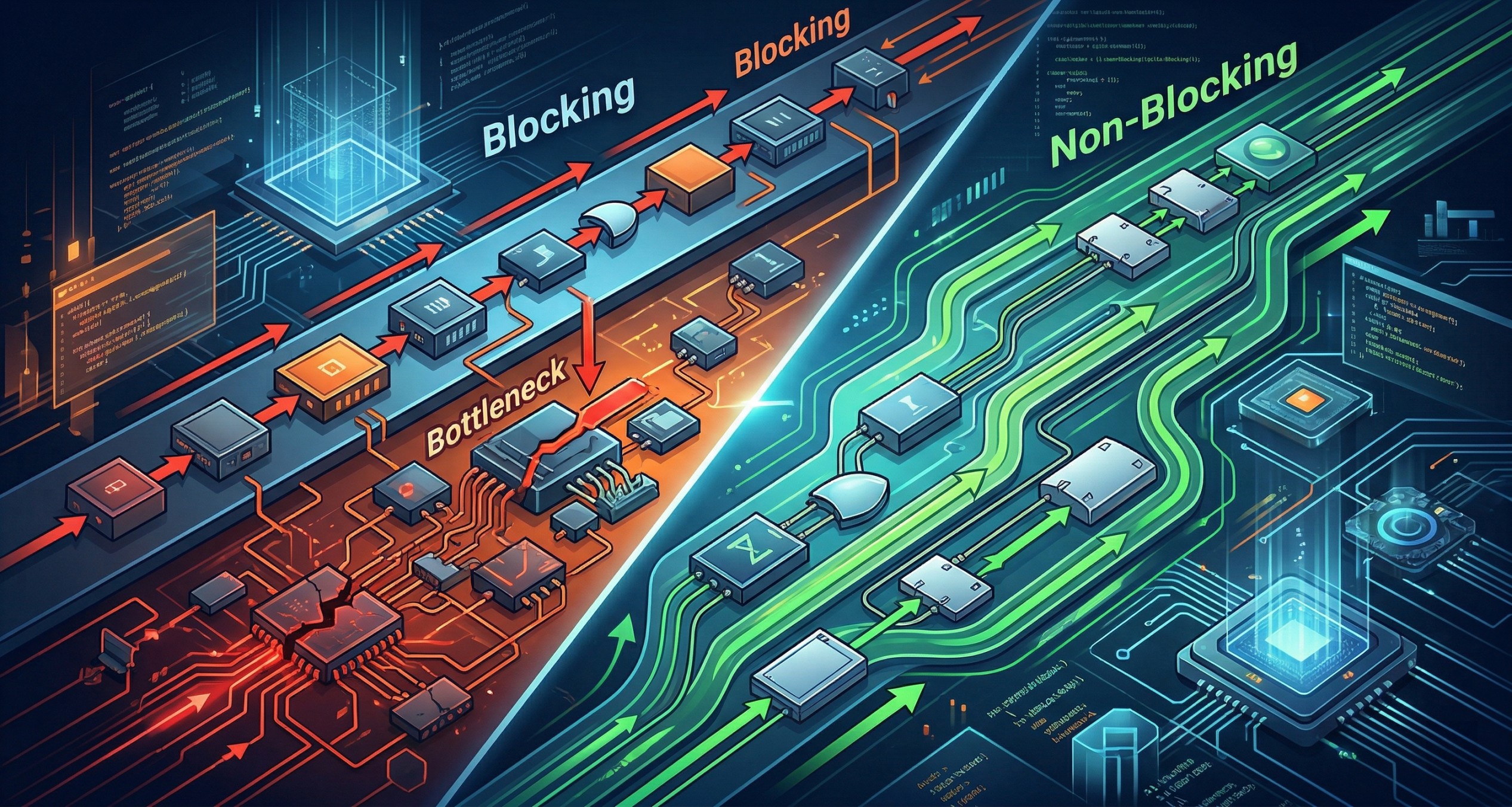

Selecting the right protocol is about matching the tool to the job. A mismatch will result in either wasted area or a system bottleneck.

| Protocol | Complexity | Throughput | Features | Ideal Use Case |

|---|---|---|---|---|

| AXI4 | High | Very High | Bursts, Out-of-Order, Separate R/W channels | CPU, DDR, DMA, PCIe |

| AHB | Medium | High | Pipelined, Bursts, Shared R/W bus | On-chip SRAM, System Backbone |

| APB | Low | Low | Simple, Low Power, Non-pipelined | Peripheral Config Registers (UART, SPI) |

| Wishbone | Flexible | Med/High | Open Source, Flexible handshake | Open-source IPs, Custom designs |

Happy coding.

fpgawizard.com